SSE3

SSE3(Streaming SIMD Extensions 3),又称PNI(Prescott New Instructions)[1],它指的是:在原有架构的处理器中,所第三次额外新增、添加的多媒体指令集,之前的两次分别是SSE、SSE2。

SSE3是Intel公司所其原有IA-32架构的处理器所研创,并在2004年初的新款Pentium 4(P4E,Prescott核心)处理器[2]中使用,之后2005年4月AMD公司也发表具备部分SSE3功效的处理器:Athlon 64(E3步进核心)[3],此后的x86处理器也几乎都具备SSE3的新指令集功能。

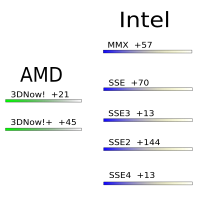

此外,在SSE3提出之前,x86架构的处理器先后已有多种多媒体指令集被提创与使用,先后顺序大致是Intel MMX、AMD 3DNow![4]、Intel SSE、Intel SSE2等。

附带一提的是,SSE3比在它之前的SSE2增加13条新指令。

新指令所带来的改变

编辑SSE3最值得一提的新功效特点,是水平式的寄存器整数运算,而在此之前的SSE、SSE2则仅能垂直运算。更进一步的特点是,指令执行时对多笔数值的同时加法运算、减法运算等,之后将结果进行存储等,都可以在单一个寄存器完成,因此SSE3可以用更简单的方式来实现同时间的多笔、大量DSP、3D性质的运算。

此外,有个新指令可将浮点数数值转换成整数数值,且进行此种转换不需要将运算切换到rounding模式,过去此类转换必须先切换至rounding模式,完成转换后再退出rounding模式,此新指令可省去此模式切换程序,使整体运算更为加速,也因此可避免邻近执行流水线(Instruction pipeline)因此而停缓、等待(模式切换会使后续执行暂停,进而减损运算性能)。

另外,新增设的LDDQU指令能够在交替加载长度不一的整数向量值时获得更佳的性能,此指令可以让Intel NetBurst架构的执行核心跨越缓存线的界线而进行数值加载。

具备SSE3硬件支持功效的处理器

编辑以下表列依据业者英文名称的字母顺序:

- AMD公司:

- Athlon 64 - 从Stepping E3的Venice(威尼斯,研发代号)以及Stepping E4的San Diego(圣地亚哥,研发代号)开始具备。

- Athlon 64 X2

- Athlon 64 FX - 从Stepping E4的San Diego(圣地亚哥,研发代号)开始具备。

- Opteron - 从Stepping E4的San Diego(圣地亚哥,研发代号)开始具备。

- Sempron - 从Stepping E3的Palermo(研发代号)开始具备。

- Turion 64

- Turion 64 X2

- Phenom

- Phenom II

- Intel公司:

- Celeron D

- Pentium 4 - 从Prescott(研发代号)开始具备。

- Pentium D

- Intel Core

- Intel Core 2

- Intel Core i7

- Xeon - 从Nocona(研发代号)开始具备。

- 全美达公司(Transmeta):

- Efficeon TM88xx(不包含型款编号为TM86xx系列的处理器)

- 威盛电子(VIA)[5]:

新增的指令

编辑共通性的指令

编辑算术指令(Arithmetic)

- ADDSUBPD - (Add-Subtract-Packed-Double)

- 输入: - { A0, A1 }, { B0, B1 }

- 输出: - { A0 - B0, A1 + B1 }

- ADDSUBPS - (Add-Subtract-Packed-Single)

- 输入: { A0, A1, A2, A3 }, { B0, B1, B2, B3 }

- 输出: { A0 - B0, A1 + B1, A2 - B2, A3 + B3 }

数组结构指令(Array Of Structures;AOS)

- HADDPD - (Horizontal-Add-Packed-Double)

- 输入: { A0, A1 }, { B0, B1 }

- 输出: { B0 + B1, A0 + A1 }

- HADDPS (Horizontal-Add-Packed-Single)

- 输入: { A0, A1, A2, A3 }, { B0, B1, B2, B3 }

- 输出: { B0 + B1, B2 + B3, A0 + A1, A2 + A3 }

- HSUBPD - (Horizontal-Subtract-Packed-Double)

- 输入: { A0, A1 }, { B0, B1 }

- 输出: { A0 - A1, B0 - B1 }

- HSUBPS - (Horizontal-Subtract-Packed-Single)

- 输入: { A0, A1, A2, A3 }, { B0, B1, B2, B3 }

- 输出: { A0 - A1, A2 - A3, B0 - B1, B2 - B3 }

- LDDQU - 如上所述,这是有交替需求时所用的指令,可以加载(load)不整齐排列的整数向量值,此指令对视频压缩的运算工作有帮助。

- MOVDDUP、MOVSHDUP、MOVSLDUP - 此三个指令是针对复杂数目需求时所用,对波形信号的运算有帮助,例如音频的声波波形处理。

- FISTTP - 类似过去x87浮点运算中的FISTP指令,不过此指令的运算执行或忽略掉浮点控制寄存器的rounding(溢绕)模式的设置,并且用“chop”(truncate,截切)模式[6]取代。允许控制寄存器忽略繁重的加载及再加载,例如C语言中将浮点数转换成整数就需要使用此种截切效果,且此种截切程序已成为C语言中的标准作法。

Intel针对SSE3所额外设计的自用指令

编辑- MONITOR、MWAIT - 此二个指令能针对多线程的应用程式进行执行优化,使处理器原有的超线程功效获得更佳的发挥。

附注说明

编辑- ^ Prescott是Intel公司产品Pentium 4处理器的项目代称,也称为研发代号。

- ^ 研发代号:Prescott。Prescott是地名也是人名,美国、英国、加拿大皆有地方取名为Prescott,另有许多人的姓氏也为Prescott,如William Prescott(美国革命指挥官)、Richard Prescott(美国革命时期的英国将军,曾两度被擒)

- ^ 研发代号:威尼斯(Venice)与圣地亚哥(San Diego)

- ^ 此外也有Cyrix公司提出的EMMI多媒体指令,不过仅短暂提出,之后并未普及使用。

- ^ 研发团队收并自美国IDT公司所100%转投资的Centaur公司

- ^ 所谓rounding模式是寄存器的内存值溢出时,溢出会使内存值归零再进行持续递增,举例而言,一个8-bit的寄存器,当其值为255时,若再加2即会变成1,就二进制来看即是11111111 + 00000010 = 00000001。而所谓chop模式是即便溢出也不归零,而持续维持在最高数值,此也称为饱和运算,即是不让其溢出归零情事发生,同样的例子,在chop模式下依旧会维持255,即是11111111 + 00000010 = 11111111。 当然,截切、饱和忽略了更多的累加值,这在多媒体运算时有其需要,当音调254阶再增个2阶、3阶,若因为溢出归零而成为0阶、1阶,就会与255阶相去甚远,相对的254阶若因饱和运算的效果最多会维持在255阶,255阶与254阶仍是相近,多媒体运算力求快速即时而不力求精确,因此些许的运算数字结果偏差仍可接受。

参考引据

编辑- X-bit Labs网站:SSE3指令集(2004年2月1日)(英文)

关连条目

编辑外部链接

编辑- Intel官方网站对SSE3的总览说明(页面存档备份,存于互联网档案馆) (英文)