张量处理单元

张量处理单元(英文:Tensor Processing Unit,简称:TPU),也称张量处理器,是 Google 开发的专用集成电路(ASIC),专门用于加速机器学习。[1]自 2015 年起,谷歌就已经开始在内部使用 TPU,并于 2018 年将 TPU 提供给第三方使用,既将部分 TPU 作为其云基础架构的一部分,也将部分小型版本的 TPU 用于销售。

| 推出年份 | 2016年5月 |

|---|---|

| 設計公司 | |

| 體系結構類型 | 神经网络 机器学习 |

总览

编辑2016 年 5 月,Google 在 Google I/O 上宣布了张量处理单元,并表示 TPU 已经在其数据中心内部使用了超过一年。[2][3]该芯片是专门为 Google 的 TensorFlow 框架(一个符号数学库,用于机器学习应用程序,如神经网络)设计的。[4]不过,截至 2017 年,Google 也将 CPU 和 GPU 用于其他类型的机器学习。[2]其他供应商也设计了自己的 AI 加速器,并针对嵌入式和机器人市场。

Google 的 TPU 是专有的,一些 TPU 的型号已经上市。在 2018 年 2 月 12 日,纽约时报报道称 Google 将“允许其他公司通过其云计算服务购买对这些芯片的访问权”。[5]Google 曾称,它们已用于 AlphaGo 与李世乭的人机围棋对战[3]以及 AlphaZero 系统中。Google还使用 TPU 进行 Google 街景中的文本处理,并且能够在不到五天的时间内找到 Google 街景数据库中的所有文本。在 Google 相册中,单个 TPU 每天可以处理超过1亿张照片。TPU 也被用在 Google 用来提供搜索结果的 RankBrain 中。[6]

与图形处理单元(GPU)相比,TPU 被设计用于进行大量的低精度计算(如 8 位的低精度)[7],每焦耳功耗下的输入/输出操作更多,但缺少用于光栅化/纹理映射的硬件。[3]

根据 Norman Jouppi 的说法,TPU 可以安装在散热器组件中,从而可以安装在数据中心机架上的硬盘驱动器插槽中。[2]

产品

编辑| TPUv1 | TPUv2 | TPUv3 | TPUv4 | Edge v1 | |

|---|---|---|---|---|---|

| 推出时间 | 2016年 | 2017年 | 2018年 | 2021年 | 2018年 |

| 制程 | 28 nm | 16 nm | 16 nm | 7 nm | |

| 裸晶尺寸/mm2 | 331 | < 625 | < 700 | < 400 | |

| 片上储存/MiB | 28 | 32 | 32 | 144 | |

| 时钟速度/MHz | 700 | 700 | 940 | 1050 | |

| 内存/GB | 8GB DDR3 | 16GB HBM | 32GB HBM | 8GB | |

| 热设计功耗/W | 75 | 280 | 450 | 175 | 2 |

| TOPS | 23 | 45 | 90 | ? | 4 |

第一代 TPU

编辑第一代TPU是一个 8 位矩阵乘法的引擎,使用复杂指令集,并由主机通过 PCIe 3.0 总线驱动。它采用28 nm工艺制造,裸晶尺寸小于 331 mm2,时钟速度为 700 MHz,热设计功耗为 28–40 W。它有28 MiB 的片上存储和 4 MiB 的 32位累加器,取 8 位乘法器的 256×256 脉动阵列的计算结果。[8]TPU 还封装了 8 GiB 的双通道 2133 MHz DDR3 SDRAM,带宽达到 34 GB/s。[9]TPU 的指令向主机进行数据的收发,执行矩阵乘法和卷积运算,并应用激活函数。[8]

第二代 TPU

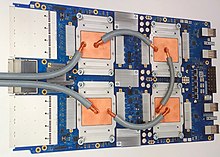

编辑第二代 TPU 于 2017 年 5 月发布。[10]Google 表示,第一代 TPU 的设计受到了内存带宽的限制,因此在第二代设计中使用 16 GB 的高带宽内存,可将带宽提升到 600 GB/s,性能从而可达到 45 TFLOPS。[9]TPU 芯片随后被排列成性能为 180 TFLOPS 的四芯片模块[10],并将其中的 64 个这样的模块组装成 256 芯片的 Pod,性能达到 11.5 PFLOPS。[10]值得注意的是,第一代 TPU 只能进行整数运算,但第二代 TPU 还可以进行浮点运算。这使得第二代 TPU 对于机器学习模型的训练和推理都非常有用。谷歌表示,这些第二代TPU将可在 Google 计算引擎上使用,以用于 TensorFlow 应用程序中。[11]

第三代 TPU

编辑第三代 TPU 于 2018 年 5 月 8 日发布。[12]谷歌宣布第三代 TPU 的性能是第二代的两倍,并将部署在芯片数量是上一代的四倍的 Pod 中。[13][14]与部署的第二代 TPU 相比,这使每个 Pod 的性能提高了 8 倍(每个 Pod 中最多装有 1,024 个芯片)。

第四代 TPU

编辑第四代 TPU 于 2021 年 5 月 19 日发布。谷歌宣布第四代 TPU 的性能是第三代的2.7倍,并将部署在芯片数量是上一代的两倍的 Pod 中。与部署的第三代 TPU 相比,这使每个 Pod 的性能提高了 5.4 倍(每个 Pod 中最多装有 4,096 个芯片)。

第五代 TPU

编辑2023年,谷歌推出了TPU v5e以及v5p。[15]

第六代 TPU

编辑2024年5月,谷歌推出了TPU v6e (Trillium)。[16]

Edge TPU

编辑参见

编辑参考文献

编辑- ^ 云张量处理单元 (TPU) | Cloud TPU. Google Cloud. [2020-07-20]. (原始内容存档于2021-06-13) (中文(中国大陆)).

- ^ 2.0 2.1 2.2 Google's Tensor Processing Unit explained: this is what the future of computing looks like. TechRadar. [2017-01-19]. (原始内容存档于2022-02-26) (英语).

- ^ 3.0 3.1 3.2 Jouppi, Norm. Google supercharges machine learning tasks with TPU custom chip. Google Cloud Platform Blog. May 18, 2016 [2017-01-22]. (原始内容存档于2016-05-18) (美国英语).

- ^ "TensorFlow: Open source machine learning" (页面存档备份,存于互联网档案馆) "It is machine learning software being used for various kinds of perceptual and language understanding tasks" — Jeffrey Dean, minute 0:47 / 2:17 from Youtube clip

- ^ Google Makes Its Special A.I. Chips Available to Others. The New York Times. [2018-02-12]. (原始内容存档于2022-04-08) (英语).

- ^ Google's Tensor Processing Unit could advance Moore's Law 7 years into the future. PCWorld. [2017-01-19]. (原始内容存档于2019-02-18) (英语).

- ^ Armasu, Lucian. Google's Big Chip Unveil For Machine Learning: Tensor Processing Unit With 10x Better Efficiency (Updated). Tom's Hardware. 2016-05-19 [2016-06-26].

- ^ 8.0 8.1 Jouppi, Norman P.; Young, Cliff; Patil, Nishant; Patterson, David; Agrawal, Gaurav; Bajwa, Raminder; Bates, Sarah; Bhatia, Suresh; Boden, Nan; Borchers, Al; Boyle, Rick; Cantin, Pierre-luc; Chao, Clifford; Clark, Chris; Coriell, Jeremy; Daley, Mike; Dau, Matt; Dean, Jeffrey; Gelb, Ben; Ghaemmaghami, Tara Vazir; Gottipati, Rajendra; Gulland, William; Hagmann, Robert; Ho, C. Richard; Hogberg, Doug; Hu, John; Hundt, Robert; Hurt, Dan; Ibarz, Julian; Jaffey, Aaron; Jaworski, Alek; Kaplan, Alexander; Khaitan, Harshit; Koch, Andy; Kumar, Naveen; Lacy, Steve; Laudon, James; Law, James; Le, Diemthu; Leary, Chris; Liu, Zhuyuan; Lucke, Kyle; Lundin, Alan; MacKean, Gordon; Maggiore, Adriana; Mahony, Maire; Miller, Kieran; Nagarajan, Rahul; Narayanaswami, Ravi; Ni, Ray; Nix, Kathy; Norrie, Thomas; Omernick, Mark; Penukonda, Narayana; Phelps, Andy; Ross, Jonathan; Ross, Matt; Salek, Amir; Samadiani, Emad; Severn, Chris; Sizikov, Gregory; Snelham, Matthew; Souter, Jed; Steinberg, Dan; Swing, Andy; Tan, Mercedes; Thorson, Gregory; Tian, Bo; Toma, Horia; Tuttle, Erick; Vasudevan, Vijay; Walter, Richard; Wang, Walter; Wilcox, Eric; Yoon, Doe Hyun. In-Datacenter Performance Analysis of a Tensor Processing Unit™. Toronto, Canada. June 26, 2017. arXiv:1704.04760 .

- ^ 9.0 9.1 Kennedy, Patrick. Case Study on the Google TPU and GDDR5 from Hot Chips 29. Serve The Home. 22 August 2017 [23 August 2017]. (原始内容存档于2021-11-23).

- ^ 10.0 10.1 10.2 Bright, Peter. Google brings 45 teraflops tensor flow processors to its compute cloud. Ars Technica. 17 May 2017 [30 May 2017]. (原始内容存档于2022-03-06).

- ^ Kennedy, Patrick. Google Cloud TPU Details Revealed. Serve The Home. 17 May 2017 [30 May 2017]. (原始内容存档于2022-06-12).

- ^ Frumusanu, Andre. Google I/O Opening Keynote Live-Blog. 8 May 2018 [9 May 2018]. (原始内容存档于2021-11-18).

- ^ Feldman, Michael. Google Offers Glimpse of Third-Generation TPU Processor. Top 500. 11 May 2018 [14 May 2018]. (原始内容存档于2021-11-18).

- ^ Teich, Paul. Tearing Apart Google's TPU 3.0 AI Coprocessor. The Next Platform. 10 May 2018 [14 May 2018]. (原始内容存档于2022-05-15).

- ^ Mirhoseini, Azalia; Goldie, Anna. A graph placement methodology for fast chip design (PDF). Nature. 2021-06-01, 594 (7962): 207–212 [2023-06-04]. PMID 35361999. S2CID 247855593. doi:10.1038/s41586-022-04657-6.

- ^ Introducing Trillium, sixth-generation TPUs. Google Cloud Blog. [2024-05-17] (美国英语).

- ^ Cloud TPU. Google Cloud. [2021-05-21] (英语).